The essentials of embedded design for Xilinx Zynq™-7000, Zynq™ MPSoC and Versal™ components

(ref.E_ZAHS)

4 days - 28 hours

Objectives

- After completing this training, you will have the necessary skills to:

- 1 - Describe the Xilinx architecture and embedded components

- 2 - Describe the various tools that comprise a Xilinx embedded design

- 3 - Select and effectively define an interface between the processor system (PS) and the programmable logic (PL)

- 4 - Design an efficient system by leveraging hardware and software resources

- 5 - Use debugging tools

- 6 - Boot your projects independently

- 7 - Maintain and update IP design based on the AXI interface and its driver

- 8 - Discover OS and write a Linux application

Prerequisites

- Digital system architecture design experience

- Basic understanding of microprocessor and FPGA architecture

- Basic understanding of C programming

- Basic HDL modeling experience

Concerned public

- Technicians and Engineers in Digital Electronics

- All our training courses are given at a distance and are accessible to people with reduced mobility.

- Our partner AGEFIPH accompanies us to implement the necessary adaptations related to your disability.

Notes

- Release date: 20/12/2021

Chapters

Objective 1

- Embedded UltraFast Design Methodology {Lecture}

- Zynq-7000 SoC Architecture Overview {Lecture}

- Zynq UltraScale+ MPSoC Architecture Overview {Lecture}

- MicroBlaze Processor Architecture Overview {Lecture}

Objective 2

- Overview of Embedded Hardware Development {Lecture}

- Driving the IP Integrator tool {Lecture, Lab}

- Overview of Embedded Software Development {Lecture}

- Driving the Vitis Tool {Lecture, Lab}

- System Debugger {Lecture, Lab}

Objective 3

- Inside the Application Processor Unit (APU) {Lecture, Lab}

- Processor Input/Output Peripherals {Lecture}

- Introduction to AXI {Lecture}

- Zynq AP SoC PS/PL AXI Interfaces {Lecture, Lab}

- AXI: Connecting AXI IP {Lecture}

- Standalone Software Platform Development {Lecture, Lab}

Objective 4

- Introduction to Interrupts {Lecture}

- Interrupts: Software Considerations {Lecture, Lab}

- Zynq Memory Resources {Lecture}

- DMA {Lecture}

- Meeting Your Performance Goals {Lecture}

- Using Linker Scripts {Lecture, Lab}

Objective 5

- Debugging the Zynq {Lecture, Lab}

Objective 6

- Zynq booting {Lecture, Lab}

Objective 7

- Using the Create and Import Wizard to Create a New AXI IP {Lecture, Lab}

- AXI BFM Simulation Using Verification {Lecture, Lab}

- Understanding Device Drivers {Lecture}

- Custom Device Drivers {Lecture, Lab}

Objective 8

- Operating Systems: Introduction and Concepts {Lecture}

- Linux: A High-Level Introduction {Lecture}

- Linux Software Application Development Overview {Lecture, Lab}

Teaching Methods

- Inter-company online training :

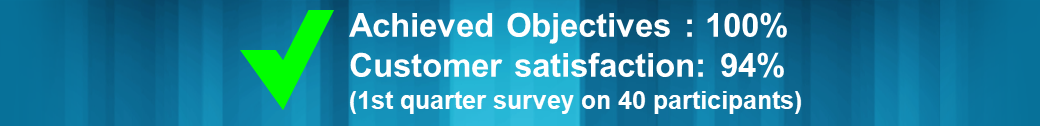

Methods of monitoring and assessment of results

- Attendance sheet

- Evaluation questionnaire

- Evaluation sheet on:

- Technical questionnaire

- Result of the Practical Works

- Validation of Objectives

- Presentation of a certificate with assessment of prior learning

Support

- Authorized Trainer Provider AMD : Engineer Electronics and Telecommunications ENSIL

- Expert AMD FPGA - Language VHDL/Verilog - RTL Design

- Expert AMD SoC & MPSoC - Language C/C++ - System Design

- Expert DSP & AMD RFSoC – HLS - Matlab - Design DSP RF

- Expert AMD Versal – AI Engines – Heteregenous System Architect

PC Recommended

- Software Configuration :

- Hardware configuration:

- Recent computer (i5 or i7)

- OS Linux 64-bits (Windows 10 compatible)

- At least 16GB RAM

- Display resolution recommended 1920x1080